# Implementing Absolute Addressing in a Motorola 68000 Processor (DRAFT)

Dylan Leigh (s3017239)

2009

This project involved the further development of a limited 68000 processor core, developed by Dylan Leigh for the subject Advanced Digital Design 1 (EEET2192) during semester 1 2008.

The CPU core originally supported only immediate and register addressing, and used one read state for each data read. This project aims to extend the system by looping the read states, allowing for absolute and more advanced addressing modes.

This document describes the CPU features and usage, including the operation of the CPU on the DE1 development board, as well as the process of implementing the new addressing mode. The development of the initial CPU design is not covered in detail.

# Contents

| Ι  | Fe   | tures and Usage                               | 4  |  |  |  |

|----|------|-----------------------------------------------|----|--|--|--|

| 1  | Fea  | ıres                                          | 4  |  |  |  |

|    | 1.1  | Current Capabilities                          | 4  |  |  |  |

|    | 1.2  | Development Tools                             | 4  |  |  |  |

| 2  | CP   | CPU Instruction Set                           |    |  |  |  |

|    | 2.1  | Move                                          | 5  |  |  |  |

|    | 2.2  | Branch                                        | 5  |  |  |  |

|    | 2.3  | Add                                           | 5  |  |  |  |

|    | 2.4  | And                                           | 5  |  |  |  |

|    | 2.5  | No-op                                         | 5  |  |  |  |

| 3  | Inte | face with DE1 Board                           | 6  |  |  |  |

|    | 3.1  | Overview                                      | 6  |  |  |  |

|    |      | 3.1.1 Structural Design Notes                 | 6  |  |  |  |

|    |      | 3.1.2 Pin Assignments                         | 6  |  |  |  |

|    | 3.2  | Using the Interface                           | 6  |  |  |  |

|    |      | 3.2.1 Outputs                                 | 7  |  |  |  |

|    | _    |                                               |    |  |  |  |

| II | D    | velopment                                     | 8  |  |  |  |

| 4  | Des  |                                               | 8  |  |  |  |

|    | 4.1  | Early Component Design                        | 8  |  |  |  |

|    | 4.2  | Final Component Design                        | 8  |  |  |  |

|    | 4.3  | Initial Fetch-Decode-Execute Cycle States     | 9  |  |  |  |

|    | 4.4  | Instruction Decoder                           | 9  |  |  |  |

|    | 4.5  | MMU and Buses                                 | 9  |  |  |  |

|    | 4.6  | Design for Absolute Addressing                | 10 |  |  |  |

|    |      | 4.6.1 Final Fetch-Decode-Execute Cycle States | 10 |  |  |  |

| 5  | Imp  | ementation Notes                              | 11 |  |  |  |

|    | 5.1  | Debugging                                     | 11 |  |  |  |

| 6  | Tes  | $\mathbf{n}\mathbf{g}$                        | 12 |  |  |  |

|    | 6.1  | Sample Programs                               | 12 |  |  |  |

|    |      | 3.1.1 Move/Add/Branch Test                    | 12 |  |  |  |

|    |      | 3.1.2 Move Flag and Branch Test               | 12 |  |  |  |

|    |      | 3.1.3 Move/And/Branch Test                    | 12 |  |  |  |

|    |      | 3.1.4 Absolute Addressing Test                | 12 |  |  |  |

|    | 6.2  | Simulation Waveforms                          | 13 |  |  |  |

|    |      | 3.2.1 Move/Add/Branch Test                    | 13 |  |  |  |

|    |      | 5.2.2 Move Flag and Branch Test               | 14 |  |  |  |

|    |      | 5.2.3 Move/And/Branch Test                    | 15 |  |  |  |

|    |      | 6.2.4 Absolute Addressing Test                |    |  |  |  |

|    |      |                                               |    |  |  |  |

| 7            | Future Development |                                     |           |  |

|--------------|--------------------|-------------------------------------|-----------|--|

|              | 7.1                | Hardware RAM                        | 17        |  |

|              | 7.2                | Instruction Set                     | 17        |  |

|              | 7.3                | Extended addressing modes           | 17        |  |

|              | 7.4                | Parameterizing memory access        | 17        |  |

|              | 7.5                | System Mode instructions            | 17        |  |

| II           | I A                | Appendices                          | 18        |  |

| A            | App                | pendix A: CPU Source Code           | 18        |  |

|              | A.1                | m68k_cpu_core.vhd                   | 18        |  |

| В            | App                | pendix B: DE1 Interface Source Code | 32        |  |

|              | B.1                | m68k_de1.vhd                        | 32        |  |

|              | B.2                | hex7seg.vhd                         | 37        |  |

|              | B.3                | clockdiv.vhd                        | 38        |  |

| $\mathbf{C}$ | App                | pendix C: Test MMU Files            | 40        |  |

|              | C.1                | m68k_fakemmu_1.vhd                  | 40        |  |

|              | C.2                | m68k_fakemmu_2.vhd                  | 43        |  |

|              | C.3                | m68k_fakemmu_3.vhd                  | 45        |  |

|              | C.4                | m68k_fakemmu_4.vhd                  | 48        |  |

| D            | App                | pendix D: Makefile                  | 51        |  |

| E            | App                | pendix E: Timing and Performance    | <b>52</b> |  |

|              | E.1                | Timing                              | 52        |  |

|              | E.2                | Logic Elements Used                 | 52        |  |

|              | E.3                | CPU Performance                     | 52        |  |

#### Part I

# Features and Usage

#### 1 Features

#### 1.1 Current Capabilities

The CPU described here implements 5 instructions from the Motorola 68000 instruction set:

- Move (MOVE),

- Branch Always (BRA),

- Add (ADD),

- Logical And (AND),

- No Operation (NOP).

The implementation supports data register, address register, immediate and absolute addressing for these instructions. The CPU is completely orthogonal; all operations can be used with all addressing modes<sup>1</sup>.

8 Data registers and 8 Address registers can be read from and written to. Although no currently implemented instructions read them the 5 user mode flags - Carry (C), Overflow (O), Negative (N), Zero (Z) and Sign Extend (X) - are implemented and are set by relevant operations.

This implementation has an an added CPU panic feature. On any invalid, illegal or unimplemented instruction or addressing mode, the CPU will set the "panic" line high and halt until the CPU has been manually reset. In simulation an assertion will be raised describing the error.

A DE1 interface entity<sup>2</sup> which allows demonstration and examination of the CPU on the DE1 boards is also provided. This board uses the Cyclone II EP2C20F484C7 FPGA device.

#### 1.2 Development Tools

The open source **GHDL** compiler (http://ghdl.free.fr/) was used for most of the EEET2192 development and the initial testing. Once all the operations had been tested successfully in simulation the system was synthesized using Quartus and tested on real hardware. The new version with absolute addressing has been developed using GHDL only and has not been tested in hardware.

The GHDL development flow is similar to using GCC or similar command line compilers. A VHDL file is analyzed to produce an object file based on an entity. This can then be linked with other object files - including, optionally, object files compiled from other sources, such as C or C++ code - to produce a native executable binary. The binary is then run to simulate the system. Assertions and reports print data to the console, and the program can optionally write a VCD or GHW waveform file.

GTKWave (http://gtkwave.sourceforge.net/) was used to view the output waveforms from the simulations, and to produce the waveform diagrams used in this document.

GNU or BSD Make (http://www.gnu.org/software/make/) can be used to automate this build and execution process. A makefile is provided in the Appendix<sup>3</sup> which builds all code and runs the three sample 68000 programs - simply executing "make" at the command line will suffice. The entire build process takes less than a second to build the CPU with GHDL on a typical desktop system, whereas analysis and synthesis under Quartus takes approximately 25 seconds, and the full build process can take minutes.

<sup>&</sup>lt;sup>1</sup>Read only locations and modes (such as immediate addressing) cannot be used for the destination.

$<sup>{}^{2}</sup>$ Refer to Section 3 on page 6.

<sup>&</sup>lt;sup>3</sup>Section D on page 51.

#### 2 CPU Instruction Set

For more information on each instruction refer to *The M68000 Programmer's Reference Manual*, 5th ed, 1979-1986 Motorola Inc., ISBN 0-13-541475-X. A complete discussion of each operation is beyond the scope of this report.

This section describes what each instruction does in this implementation; the full 68000 implements more instructions and addressing modes.

Note that due to limitations of the "Fake MMU" simulated RAM entities used for testing, the "RAM" cannot be written to, although the CPU design itself supports writes to RAM.

#### 2.1 Move

- Identified by "0001", "0010" or "0011" at the start of the instruction, depending on data size.

- Copies 8, 16 or 32 bits of data from a register, memory location or a constant to a register.

- Sets Zero and Negative flags if the data copied is zero or negative.

#### 2.2 Branch

- Identified by "0110" at the start of the instruction.

- Performs an 8 or 16 bit signed addition on the program counter. For 8 bit data the offset is encoded in the instruction itself; 16 bit data is read in a similar manner to immediate addressing.

- Changes no flags.

#### 2.3 Add

- Identified by "1101" at the start of the instruction.

- Performs an addition of 8+8, 16+16 or 32+32 bits of data. One of the operands (which the data is saved in) must be a data register, but the other can be a memory location, immediate data or an address or data register.

- Sets Zero and Negative flags if the data copied is zero or negative.

- Note that this operation should set the Carry and Overflow flags, however this requires a proper ALU component to be implemented which could not be completed due to time constraints. See the "Planned Features not Fully Implemented" section<sup>4</sup>.

#### 2.4 And

- Identified by "1100" at the start of the instruction.

- Performs a logical and of 8, 16 or 32 bits of data. One of the operands (which the data is saved in) must be a data register, but the other can be a memory location, immediate data or an address or data register.

- Sets Zero and Negative flags if the data copied is zero or negative.

#### 2.5 No-op

- Identified by "0100111001110001" as the instruction.

- Performs no changes (other than changing the PC during the fetch cycle).

- Changes no flags.

<sup>&</sup>lt;sup>4</sup>Section ?? on page ??.

#### 3 Interface with DE1 Board

The source code for this interface is in the Appendix, section B.1 on page 32.

#### 3.1 Overview

The DE1 interface component allows examination and testing of the CPU implementation on the DE1 board and includes the following facilities:

- "MMU" with 4 sample programs (see Testing<sup>5</sup>).

- Display of flags, lower byte of address and data buses and CPU/MMU outputs including MMU requests and the panic line.

- Manually operated clock and free running clock with selectable speeds.

#### 3.1.1 Structural Design Notes

The interface file includes the code for links between the CPU outputs and the board lights, and the CPU itself is a component of the interface. The interface also contains the behavior of the MMU itself, a nested set of case statements which put different values on the data bus depending on the address bus and the program selected.

The hex display logic was previously used in the EEET2192 laboratories and is included verbatim. The source can be found in the Appendix $^6$ .

The adjustable divider used to change the speed of the clock was modified from code used in the EEET2192 laboratories, which was itself a modified version of the behavioral counter code from the lab 2 specification. Source for this file is also located in the Appendix<sup>7</sup>.

#### 3.1.2 Pin Assignments

As this component is not intended for use with other boards, to simplify assignments the names of board pins were used directly as port names. The standard DE1 pin assignments were used.

#### 3.2 Using the Interface

Initialization:

- Set switch 0 off to disable the free running clock.

- Choose the test program with switches 9 and 8:

- 00: Test move, add and branch.

- 01: Test move flag setting and branch.

- 10: Test move, and and branch.

- 11: Test absolute addressing.

- Reset the CPU with key 3.

At this point the CPU can be traced using the manual clock, key 0. To use the free running clock:

- Choose speed with switches 3 to 1.

- Activate the clock with switch 0.

- The clock speed can be changed and the clock can be stopped and started at any time.

<sup>&</sup>lt;sup>5</sup>Section 6 on page 12.

<sup>&</sup>lt;sup>6</sup>Section B.2 on page 37.

<sup>&</sup>lt;sup>7</sup>Section B.3 on page 38.

#### 3.2.1 Outputs

The following outputs are displayed on the DE1 board LEDs:

- Hex digits 2 and 3 show the lower byte of the address bus. This is usually the location of the last memory access, or the PC minus 2.

- Hex digits 0 and 1 show the lower byte of the data bus. Note that the data bus is cleared after a request has been fulfilled, so data may only show up here for one or two clock cycles.

- Red LED 9 hows the panic line. If this is lit the CPU has halted and must be restarted with the reset (key 3).

- Red LED 4 shows the clock signal.

- Red LED 1 indicates the bus read-write line is high. This may appear on initialization or briefly on reset, but should not be lit for any sample programs.

- Red LED 0 indicates a bus request (i.e. the CPU has requested the MMU put the data at the address bus location on the data bus).

- Green LED 7 is lit by the MMU when the bus request has been fulfilled.

- Green LEDs 6 and 5 show the bus data size. For all sample programs word or byte data is used; as immediate byte data is packed into a word all requests from the sample programs will be word length "10".

- Green LEDs 4 to 0 show the CPU flags:

- 4 is X (sign extend) (never lit by implemented operations)

- 3 is N (negative) (lit by some operations)

- 2 is Z (zero) (lit by some operations)

- 1 is V (overflow) (never lit by implemented operations)

- 0 is C (carry) (never lit by implemented operations)

#### Part II

# Development

## 4 Design

#### 4.1 Early Component Design

This is the initial design from the EEET2192 project.

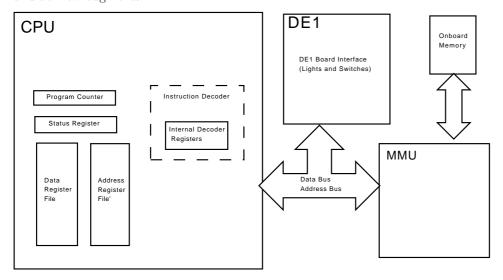

#### 4.2 Final Component Design

This represents the final design from the EEET2192 project and this project. Not all ports or registers are shown explicitly on this diagram - for example, the buses include several control lines used to signal requests and acknowledgments.

Instead of using a separate ALU entity, all arithmetic operations are performed using VHDL operators in the CPU entity, simplifying the implementation. The synthesizer made use of the dedicated logic elements on the FPGA chip for these instructions.

The onboard memory access was not implemented and instead four "Fake MMU" entities<sup>8</sup> simulate memory reads for four different sample programs. These can be selected from the DE1 interface. In simulation these entities will raise a warning if there is an attempt to read from a location that should not be required by the program.

<sup>&</sup>lt;sup>8</sup>Source code for these entities is in section C on page 40.

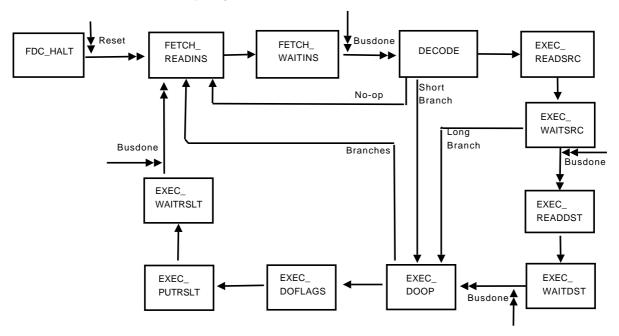

#### 4.3 Initial Fetch-Decode-Execute Cycle States

This diagram shows the CPU's fetch-decode-execute cycle from the EEET2192 project, when the only addressing modes implemented were immediate and register.

The labelled double arrows with incoming double arrow indicate a signal which must be received for that state to advance. The plain labelled arrows indicate the state flow for a particular operation (which does not follow the common state flow at that point).

Note that moving to the FDC\_HALT state is not shown. Any illegal operations (including trying to run unimplemented operations or operations with unimplemented addressing modes) result in the CPU panic line being set high and the CPU changing to he FDC\_HALT state until it is reset manually.

The final CPU state cycle design is provided in section 4.6.1 on the following page.

#### 4.4 Instruction Decoder

The instruction decoder is wholly contained within the CPU code. Due to the tight integration with the CPU no attempt was made to implement it as a separate component.

The decoder determines the current operation, and saves it to a state register. Any data sizes and addressing modes are determined and saved in separate CPU-internal registers, in a format common to most 68000 operations. These registers are read in later execute cycle states to allow common data fetching and saving procedures to be performed using operation-agnostic code.

#### 4.5 MMU and Buses

Initially the implementation was intended to use real hardware RAM, which would be initialized with a program and which could be written to (see the "Early Component Design" above<sup>9</sup>).

Due to lack of time a real MMU component could not be completed, and the implementation instead has read only "memory", which is emulated by a fake MMU which uses a case statement on the address bus to put different values on the data bus. 4 sample programs were written and assembled which test various CPU instructions and addressing modes. These may be selected in the DE1 board interface<sup>10</sup> or run in simulation<sup>11</sup>.

<sup>&</sup>lt;sup>9</sup>Section 4.1 on the previous page.

$<sup>^{10}</sup>$ Section 3 on page 6.

<sup>&</sup>lt;sup>11</sup>Section 6 on page 12.

#### 4.6 Design for Absolute Addressing

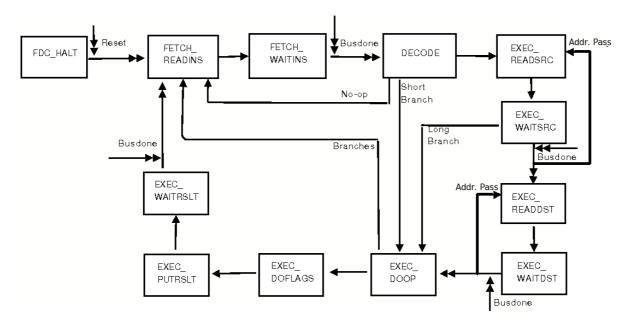

For absolute addressing memory reads, it is necessary for the CPU to make two reads from memory - one to get the address, and another to get the data from that address.

The original CPU state cycle design allowed for only one read and wait. The new design "loops" these states, using a new register to keep track of how many passes have been completed. This design supports up to three passes, which will be sufficent to allow all addressing modes on the 68000 to be implemented.

#### 4.6.1 Final Fetch-Decode-Execute Cycle States

## 5 Implementation Notes

Implementation was straightforward, with a new test program developed<sup>12</sup> to test the new addressing mode. The new CPU core has not yet been tested in hardware.

#### 5.1 Debugging

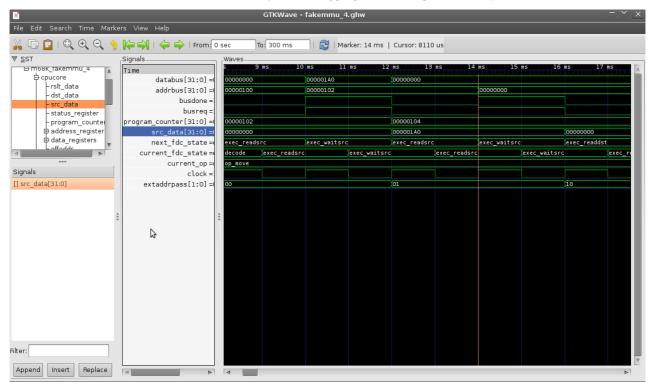

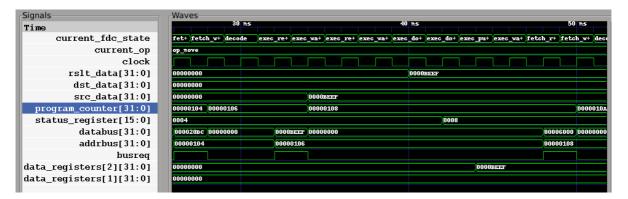

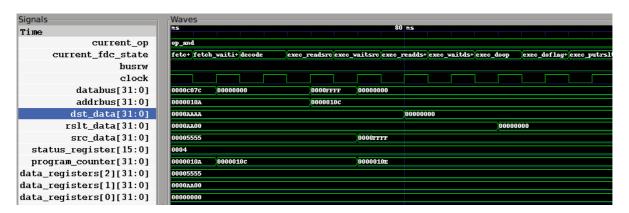

The GTKWave software was used extensively for debugging and testing. An example is shown below:

One error found late during development is shown above. Sample program 4<sup>13</sup> was being run to test absolute addressing mode, and Fake MMU 4 was warning that at 14ms, a memory request was made for an unhandled location (i.e. one which the program should not have accessed during normal operation).

As can be seen in the screenshot, the CPU was requesting a read of location \$0, instead of the data at \$140. Tracing through the CPU code it was found that the address for the second memory request was being taken directly from the data bus, instead of the SRC\_DATA internal register. The \$140 had already been recieved, acknowledged and placed in the SRC\_DATA register. Transferring SRC\_DATA to the address bus during the second EXEC\_READSRC pass fixed the error.

<sup>&</sup>lt;sup>12</sup>See section 6.1.4 on the following page.

$<sup>^{13}</sup>$ Assembly source code for the program is in section 6.1.4 on the next page; the corresponding MMU source code is in section C.4 on page 48.

## 6 Testing

Most parts of the system were developed using the open source GHDL compiler (see Design Tools<sup>14</sup>), which builds test-benches as native binary applications. These applications will simulate the system and output relevant assertions and reports. They can also generate waveform files.

Four sample assembly programs were written which use various features of the implemented CPU. These were encapsulated within "fake" MMU programs which set the data bus to the machine code values of the program when the CPU requested them. These programs also reset the system when starting and provided a clock signal to operate the CPU.

The VHDL source for the MMU programs is in the Appendix<sup>15</sup>; the assembly programs themselves are provided below.

#### 6.1 Sample Programs

Annotated simulation waveforms for these programs can be found in section 6.2 on the next page.

#### 6.1.1 Move/Add/Branch Test

```

org $100

move.w #02, d1

move.w #03, d2

add.w d2, d1

add.w #5, d0; note d0 will continue increasing while program loops

bra $100

end

```

#### 6.1.2 Move Flag and Branch Test

```

org $100

move.w #0, d1 ; sets zero flag

move.w #BEEF, d2 ; sets negative flag

bra $100

end

```

#### 6.1.3 Move/And/Branch Test

```

org $100

move.w #$AAAA, d1

move.w #$5555, d2

and.b d2,d1; sets zero flag

and.w $#FFFF, d0

bra $100

end

```

#### 6.1.4 Absolute Addressing Test

```

org $100

move.w $10A, d1

move.w $1BB, d2

bra $100

org $10A

dw $1111

org $1BB

dw $2222

end

```

<sup>&</sup>lt;sup>14</sup>Section 1.2 on page 4.

<sup>&</sup>lt;sup>15</sup>Section C on page 40.

#### 6.2 Simulation Waveforms

These images were produced using GTKWave (see Tools, section 1.2 on page 4). A full set of waveforms would be too large to include in this report. A selected number which show state and register transitions have been included. The source code for the assembly programs running on the CPU during these tests is in section 6.1 on the previous page.

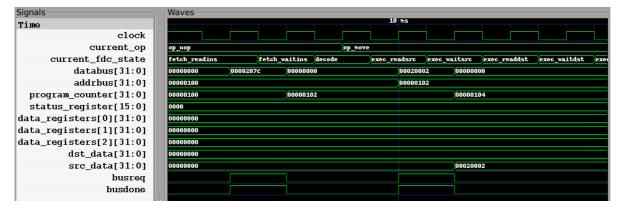

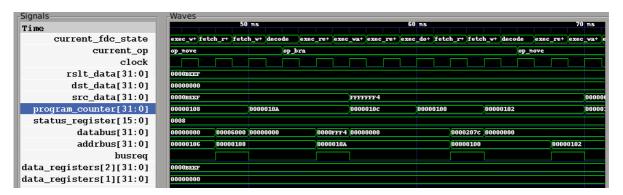

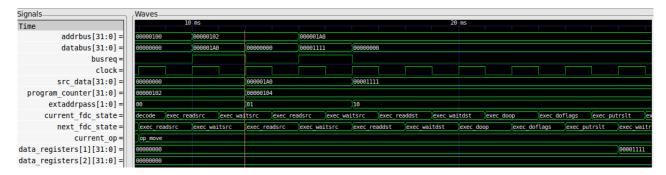

#### 6.2.1 Move/Add/Branch Test

This is just after reset (note the current\_op is no-op until the first instruction is decoded). The instruction is fetched and the program counter incremented by 2, and then immediate data is fetched from the PC location (and the PC is incremented again). Note that the destination is a data register so there are no memory requests and no activity during the destination read states.

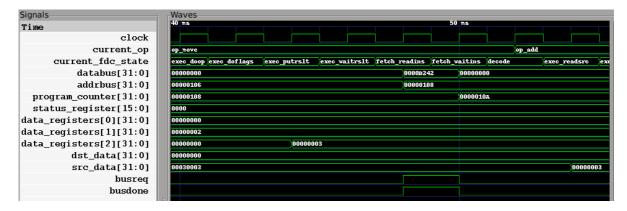

This screenshot shows the end of the move instruction. The data is written to the destination (in this case, data register 2) during the EXEC\_PUTRSLT cycle. The next instruction is an add and we can see it decoded here. The operands are registers so we do not see any memory accesses until the source data is placed into the CPU internal src\_data register.

This screenshot shows the execution of the add instruction. The source and destination - both data registers - are read into the src\_data and dst\_data internal registers. During the EXEC\_DOOP cycle these are added and

the result is placed in the internal rslt\_data register. This is saved to the destination during the EXEC\_PUTRSLT cycle.

#### 6.2.2 Move Flag and Branch Test

| Signals                 | Waves                                                                           |                                       |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| Time                    | 10 ms 20                                                                        | 0 ms                                  |  |  |  |  |

| current_fdc_state       | fetch_readi+ fetch_w+ decode exec_re+ exec_wa+ exec_re+ exec_wa+ exec_do+ exec_ | c_do+_exec_pu+_exec_wa+_fetch_r+_fetc |  |  |  |  |

| current_op              | op_nop op_move                                                                  |                                       |  |  |  |  |

| clock                   |                                                                                 |                                       |  |  |  |  |

| rslt_data[31:0]         | 00000000                                                                        |                                       |  |  |  |  |

| dst_data[31:0]          | 00000000                                                                        |                                       |  |  |  |  |

| src_data[31:0]          | 00000000                                                                        |                                       |  |  |  |  |

| program_counter[31:0]   | 00000100 00000102 00000104                                                      |                                       |  |  |  |  |

| status_register[15:0]   | 0000                                                                            | 0004                                  |  |  |  |  |

| databus[31:0]           | 00000000 0000207c 00000000                                                      | 000020вс                              |  |  |  |  |

| addrbus[31:0]           | 00000100 00000102                                                               | 00000104                              |  |  |  |  |

| busreq                  |                                                                                 |                                       |  |  |  |  |

| data_registers[2][31:0] | 00000000                                                                        |                                       |  |  |  |  |

| data_registers[1][31:0] | 00000000                                                                        |                                       |  |  |  |  |

|                         |                                                                                 |                                       |  |  |  |  |

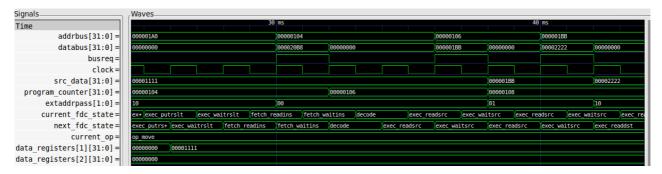

This screenshot shows the first instruction, which moves the immediate value 0 to d1. As the value is zero, the initial value of the data bus, we cannot see it being put on the data bus (although the PC is incremented when the immediate data is read). As d1 is also already zero, we do not see this change. However, during the EXEC\_DOFLAGS cycle we can see bit 3 of the status register is set, indicating the last instruction generated a zero result.

The second move, \$BEEF to d2, is visible here. We can see the instruction being read, decoded, the immediate value being read and placed in the src\_data internal register, and then in the rslt\_data register. The status register changes from 4 to 8, indicating that now the negative flag is set - as a 16 bit value \$BEEF is a negative number.

The full set of cycles for a long branch instruction can be seen here. After the instruction is decoded the next word is read (\$FFF4 or -12 decimal). This is sign extended to 32 bits (the \$FFFFFFF4 in src\_data) and added to the program counter in the EXEC\_DOOP state, returning it to the start of the program (\$100). We can see that in a branch the next instruction starts immediately - state after EXEC\_DOOP is FETCH\_READINS, normally it would be EXEC\_PUTRSLT.

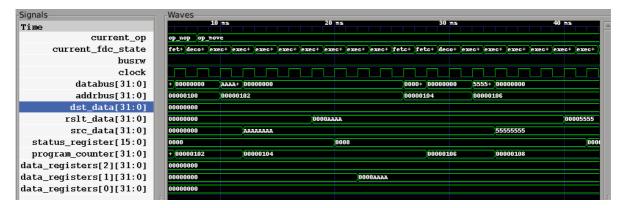

#### 6.2.3 Move/And/Branch Test

This screenshot shows the first two instructions, which move \$AAAA and \$FFFF into d1 and d2.

The next instruction is a byte size and operation on d1 and d2 - and 1010 with 0101. The lower byte is set to 0 and the zero flag is set.

The next instruction is an and with immediate data (\$FFFF) and d0 (0), again producing zero.

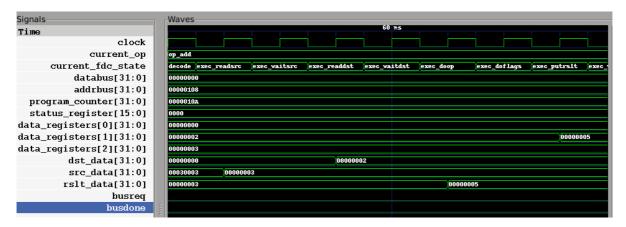

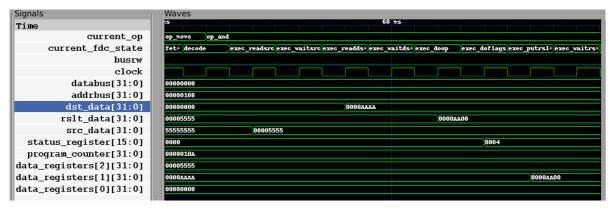

#### 6.2.4 Absolute Addressing Test

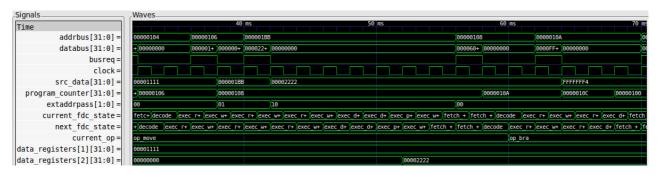

This screenshot shows the source read states (EXEC\_READSRC and EXEC\_WAITSRC) looping to fetch the address of the data from \$102 (pass 1 - EXTADDRPASS changes from 00 to 01) and then again to fetch the data from that address (at \$1A0 - EXTADDRPASS changes from 01 to 10).

The data from \$1A0 is put into d1 during the EXEC\_PUTRSLT state. When the CPU cycle restarts, EXTADDRPASS is reset to 00 (during the FETCH\_READINS state). To the left of this screenshot we can see the start of the next move instruction where EXTADDRPASS is again used in a pair of EXEC\_READSRC and EXEC\_WAITSRC states. The address \$1BB is read from location \$106 (within the program code) and the data \$2222 is read from address \$1BB.

At the end of the second move instruction \$2222 is loaded into data register 2. At the end of this diagram the branch instruction is executing and the PC returns to the start of the program (location \$100).

# 7 Future Development

- 7.1 Hardware RAM

- 7.2 Instruction Set

- 7.3 Extended addressing modes

#### 7.4 Parameterizing memory access

It may be advantageous to replace the memory access states (see the state diagram <sup>16</sup>) with a single pair of access-wait states which are parametrized depending on the addressing mode. This would allow the same code to be used for immediate and absolute addressing for source and destination, as well as more advanced modes such as register indirect.

### 7.5 System Mode instructions

$<sup>\</sup>overline{\ }^{16}$ Section 4.3 on page 9.

#### Part III

# **Appendices**

# A Appendix A: CPU Source Code

#### A.1 m68k\_cpu\_core.vhd

```

-- CPU core for 68k

— Dylan Leigh s3017239

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity m68k_cpu_core is

port (

9

reset: in std_logic; — active high

clock: in std_logic;

panic: out std_logic; — set high when CPU panics and halts

13

— nothing changes until manually reset

— bus controls

busrw: out std_logic; — bus read/write: zero is write

busreq: out std_logic; — set to 1 to make a request from the MMU

busdone: in std_logic; — is set to 1 when request fulfilled by the MMU

busdatasize: out std_logic_vector(1 downto 0);

— 68k convention: 01: byte (8), 10: word(16), 11: long (32)

21

— address bus

addrbus: out std_logic_vector(31 downto 0);

– data bus

25

databus: in std_logic_vector(31 downto 0);

— memory writes TODO databus: inout std_logic_vector(31 downto 0)

— for debugging

29

flags: out std_logic_vector(4 downto 0)

end m68k_cpu_core;

33

architecture behaviour of m68k_cpu_core is

35

type FDC_State_Type is (FETCH_READINS, FETCH_WAITINS,

DECODE,

37

— note source or destination may be immediate data,

— which still has to be read from memory (and

— waited on)

EXEC_READSRC, EXEC_WAITSRC, — EXEC_PUTSRCALU,

41

{\sf EXEC\_READDST}, \ \ {\sf EXEC\_WAITDST}, \ \ --- \ \ {\sf EXEC\_PUTDSTALU},

EXEC_DOOP, EXEC_DOFLAGS,

EXEC_PUTRSLT, EXEC_WAITRSLT,

FDC_HALT);

signal current_fdc_state , next_fdc_state : FDC_State_Type;

-- Note we are using "instruction" to refer to the whole thing

-- including operands and "opcode" to refer to the opcode part.

49

"Operation" is what the opcode represents

— internal use only

```

```

type CPUOp is (OP_MOVE, OP_ADD, OP_AND, OP_BRA, OP_NOP);

signal current_op: CPUOp;

53

signal current_inst: std_logic_vector(15 downto 0);

signal opdatasize: std_logic_vector(1 downto 0);

57

— effective address codes, either copied directly from the instruction or

-- determined from it during decode

— internal use only

signal src_addrcode: std_logic_vector(5 downto 0);

61

signal dst_addrcode: std_logic_vector(5 downto 0);

- internal use only - set for the second memory access

— pass, for extended adressing TODO

signal extaddrpass: std_logic_vector(1 downto 0);

65

-- internal use only - effective address location

signal effaddr: std_logic_vector(31 downto 0);

-- programmer registers

69

-- TODO: these should be replaced later with clocked registers

type RegisterSet is array (0 to 7) of std_logic_vector(31 downto 0);

signal data_registers: RegisterSet;

signal address_registers: RegisterSet;

73

signal program_counter: std_logic_vector(31 downto 0);

signal status_register: std_logic_vector(15 downto 0);

75

-- internal registers

77

signal src_data: std_logic_vector(31 downto 0);

signal dst_data: std_logic_vector(31 downto 0);

signal rslt_data: std_logic_vector(31 downto 0);

81

TODO component registers

83

flags <= status_register(4 downto 0);</pre>

85

fdc_activity: process (reset, clock) — busdone for wait states TODO

begin

if reset = '1' then

89

-- XXX: SET INTER-CYCLE SIGNALS AND ALL OUTPUTS TO KNOWN

INITIAL VALUES HERE

91

program_counter <= x"00000100";</pre>

status\_register <= x"0000";

next_fdc_state <= FETCH_READINS;</pre>

95

-- Starting from fetch state the instruction decoding signals

— should not affect anything but are included here anyway

current_op <= OP_NOP;</pre>

current_inst <= x"0000";

99

opdatasize <= "10"; -- word

src\_addrcode <= "000000"; -- d0

101

dst_addrcode <= "000000"; -- d0</pre>

extaddrpass <= "00";

103

src_data <= x"00000000":

dst_data \le x"00000000";

rslt_data <= x"000000000";

107

for i in 0 to 7

loop

data\_registers(i) \le x"00000000";

end loop;

111

```

```

addrbus <= x"00000100";

— TODO no mem writes databus <= x"00000000";</p>

busreq \ll '0';

115

busrw <= '0';

busdatasize <= "00";</pre>

117

panic \leq '0';

119

else --- set next state based on current state

start huge current state statement of doom

121

if rising_edge(clock) then

case current_fdc_state is

when FETCH_READINS =>

125

addrbus <= program_counter;

busrw <= '0'; —read

127

busdatasize <= "10"; --word size

busreq <= '1'; --request

129

next_fdc_state <= FETCH_WAITINS;</pre>

extaddrpass <= "00";</pre>

131

when FETCH_WAITINS =>

133

if busdone = '1' then

program_counter <= std_logic_vector(</pre>

135

unsigned(program_counter) + 2);

busreq <= '0'; ---end request

137

current_inst <= databus(15 downto 0);</pre>

next_fdc_state <= DECODE;</pre>

end if; — busdone

141

when DECODE =>

— start outer big decode case statement

-\!- Note - this is more complex than just one case statement on

— one set of bits as some operations only have 2 unique bits,

145

— and some have 8 unique bits

case current_inst(15 downto 12) is

- TODO when "0000" \Longrightarrow -- cmpi (immediate)

-- current_op <= OP_CMPI;</pre>

149

-- TODO decode effective addresses

-- next_fdc_state <= EXEC_READSRC;</pre>

when "0001" \Longrightarrow — move.b

153

{\tt current\_op} \: <= \: \mathsf{OP\_MOVE} \colon

opdatasize <= "01"; --- byte

155

— decode effective addresses

src_addrcode <= current_inst(5 downto 0);</pre>

157

dst_addrcode <= current_inst(11 downto 6);</pre>

next_fdc_state <= EXEC_READSRC;</pre>

159

when "0010" \Longrightarrow — move.w

161

current_op <= OP_MOVE;</pre>

opdatasize <= "10"; -- word

163

decode effective addresses

src_addrcode <= current_inst(5 downto 0);</pre>

165

dst_addrcode <= current_inst(11 downto 6);</pre>

next_fdc_state <= EXEC_READSRC;</pre>

167

when "0011" \Longrightarrow — move. I

169

current_op <= OP_MOVE;</pre>

opdatasize <= "11"; -- long

171

decode effective addresses

src_addrcode <= current_inst(5 downto 0);</pre>

173

```

```

dst_addrcode <= current_inst(11 downto 6);</pre>

next_fdc_state <= EXEC_READSRC;</pre>

175

when "0100" \Longrightarrow — nop

if current_inst(11 downto 0) = "111001110001"

then -- no-op

179

current_op <= OP_NOP;</pre>

next_fdc_state <= FETCH_READINS;</pre>

else — PANIC due to unimplemented opcode

next_fdc_state <= FDC_HALT;</pre>

183

panic <= '1';

report "CPU Panic — unimplemented opcode"

185

severity FAILURE;

end if:

187

when "0110" \Longrightarrow — branch

if current_inst (11 \text{ downto } 8) = "0000"

then — branch

191

current_op <= OP_BRA:</pre>

-- decode destination

193

if current_inst(7 downto 0) = x''00''

then — 16 bit branch — read another word

195

src_addrcode <= "111100"; -- immediate</pre>

next_fdc_state <= EXEC_READSRC;</pre>

197

else — 8 bit branch — handle here

if current_inst(7) = '1'

199

then — sign extend

src_data <= x"FFFFFF" & current_inst(7 downto</pre>

201

0);

else

src_data <= x"000000" & current_inst(7 downto</pre>

end if; — sign extend

next_fdc_state <= EXEC_DOOP;</pre>

205

end if; — 8 bit destination

207

else -- PANIC due to unimplemented opcode

next_fdc_state <= FDC_HALT;</pre>

209

panic \ll '1';

report "CPU Panic - unimplemented opcode"

211

severity FAILURE;

end if:

— TODO when "1011" \Rightarrow — cmp (not immediate)

215

-- current_op <= OP_CMP;</pre>

-- TODO decode effective addresses

-- next_fdc_state <= EXEC_READSRC;</pre>

219

when "1101" \Rightarrow --- add.b/w/l

current_op <= OP_ADD;</pre>

— detemines source dest order of operands

if (current_inst(8) = '1')

223

then

next_fdc_state <= FDC_HALT;</pre>

225

panic \ll '1';

report "CPU Panic - unimplemented adressing mode"

227

severity FAILURE;

else

opdatasize <= current_inst(7 downto 6);

src_addrcode <= current_inst(5 downto 0);</pre>

231

-- dest is a data register

```

```

dst_addrcode <= "000" & current_inst(11 downto 9);</pre>

233

end if:

next_fdc_state <= EXEC_READSRC;</pre>

235

when "1100" \Longrightarrow — and .b/w/l

237

current_op <= OP_AND;</pre>

— decode effective addresses

239

detemines source dest order of operands

if (current_inst(8) = '1')

241

next_fdc_state <= FDC_HALT;</pre>

243

panic <= '1';

report "CPU Panic - unimplemented adressing mode"

245

severity FAILURE;

else

247

opdatasize <= current_inst(7 downto 6);</pre>

src_addrcode <= current_inst(5 downto 0);</pre>

249

-- dest is a data register

dst_addrcode <= "000" & current_inst(11 downto 9);</pre>

251

end if:

next_fdc_state <= EXEC_READSRC;</pre>

253

when others => -- PANIC due to unimplemented opcode

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

257

report "CPU Panic - unimplemented opcode"

severity FAILURE;

end case; — current inst is?

— end outer big decode case statement

261

when EXEC_READSRC => -- TODO direct memory

case src_addrcode(5 downto 3) is

when "000" \Rightarrow — data register

265

this should be replaced with an integer/unsigned

-- expression on the array index

case src_addrcode(2 downto 0) is

when "000" \Rightarrow src_data <= data_registers(0);

269

when "001" \Rightarrow src_data \ll data_registers(1);

when "010" => src_data <= data_registers(2);

when "011" => src_data <= data_registers(3);

when "100" => src_data <= data_registers(4);

273

when "101" \Rightarrow src_data <= data_registers(5);

when "110" => src_data <= data_registers(6);

when "111" \Rightarrow src_data \Leftarrow data_registers (7);

end case; — src_addrcode register section

277

next_fdc_state <= EXEC_WAITSRC;</pre>

279

when "001" \Rightarrow — address register

— this should be replaced with an integer/unsigned

281

-- expression on the array index

case src_addrcode(2 downto 0) is

283

when "000" => src_data <= address_registers(0);

when "001" => src_data <= address_registers(1);

285

when "010" => src_data <= address_registers(2);

when "011" => src_data <= address_registers(3);

287

when "100" => src_data <= address_registers(4);

when "101" \Rightarrow src_data \Leftarrow address_registers(5);

289

when "110" => src_data <= address_registers(6);

when "111" \Rightarrow src_data \Leftarrow address_registers (7);

291

end case; — src_addrcode register section

next_fdc_state <= EXEC_WAITSRC;</pre>

293

```

```

when "111" \Rightarrow -- could be immediate, absolute, offset

295

case src_addrcode(2 downto 0) is

when "000" \Longrightarrow — word addr absolute

case extaddrpass is

299

when "00" \Rightarrow

addrbus <= program_counter;

busrw <= '0'; —read

— note we don't use opdatasize as that is

303

-- the size of the final value we want not

-- the address it is at.

busdatasize <= "10";</pre>

busreq <= '1'; --request

307

next_fdc_state <= EXEC_WAITSRC;</pre>

when "01" \Rightarrow — pass 2

-- read from location we just got

311

addrbus <= src_data;</pre>

313

busrw <= '0': ---read

if opdatasize = "11"

315

then -- long

busdatasize <= "11";</pre>

317

else — word size, byte is in lower half

busdatasize <= "10";

319

end if; — datasize

busreq <= '1'; --request

321

next_fdc_state <= EXEC_WAITSRC;</pre>

323

when others =>

next_fdc_state <= FDC_HALT;</pre>

325

panic <= '1':

report "CPU Panic — bad extaddrpass"

327

severity FAILURE;

end case; — extaddrpass

329

when "001" \Rightarrow — long addr absolute

331

case extaddrpass is

when "00" \Longrightarrow

333

addrbus <= program_counter;

busrw <= '0'; —read

335

-- note we don't use opdatasize as that is

-- the size of the final valjue we want not

337

— the address it is at.

busdatasize <= "11";</pre>

339

busreq <= '1'; --request</pre>

next_fdc_state <= EXEC_WAITSRC;</pre>

341

when "01" \Longrightarrow — pass 2

read from location we just got

addrbus <= src_data;</pre>

345

busrw <= '0'; ---read

347

if opdatasize = "11"

then -- long

349

busdatasize <= "11";</pre>

else —word size, byte is in lower half

busdatasize <= "10";</pre>

end if; — datasize

353

busreq <= '1'; --request

```

```

next_fdc_state <= EXEC_WAITSRC;</pre>

355

when others =>

357

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

359

report "CPU Panic — bad extaddrpass"

severity FAILURE;

361

end case; — extaddrpass

363

when "100" \Longrightarrow — immediate

addrbus <= program_counter;</pre>

365

busrw <= '0'; --read

if opdatasize = "11"

367

then — long

busdatasize <= "11";</pre>

369

else —word size, byte is in lower half

busdatasize <= "10";</pre>

371

end if; — datasize

busreq <= '1'; --request</pre>

373

next_fdc_state <= EXEC_WAITSRC;</pre>

end when immediate

375

when others =>

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

379

report "CPU Panic - invalid addresssing mode"

severity FAILURE;

end case; — addr mode 2 downto 0

383

when others =>

next_fdc_state <= FDC_HALT;</pre>

panic \ll '1';

report "CPU Panic — unimplemented addressing mode"

387

severity FAILURE:

end case; — src_addrcode 5 downto 3

when EXEC_WAITSRC => -- TODO direct memory

391

case src_addrcode(5 downto 3) is

when "000" \Rightarrow — data register

— TODO this is necessary for the clocked registers

later

next_fdc_state <= EXEC_READDST:</pre>

395

— TODO seperate ALU next_fdc_state <= EXEC_PUTSRCALU;</p>

when "001" => -- address register clock

397

— TODO this is necessary for the clocked registers

later

next_fdc_state <= EXEC_READDST;</pre>

399

-- TODO seperate ALU next_fdc_state <= EXEC_PUTSRCALU;

401

when "111" \Longrightarrow — immediate or direct

if busdone = '1'

403

then

busreq <= 'O'; —end request

405

case src_addrcode(2 downto 0) is

when "000" => -- word absolute address

407

case extaddrpass is

when "00" \Longrightarrow — FIXME test

409

program_counter <= std_logic_vector(</pre>

unsigned (program_counter) + 2);

411

src_data <= x"0000" & databus(15 downto</pre>

0);

```

```

— set to 01 here — we've made 1 pass

extaddrpass <= "01";

415

next_fdc_state <= EXEC_READSRC;</pre>

417

when "01" \Longrightarrow — FIXME test

if current_op = OP_BRA

419

then

-- sign extend

421

src_data <= x"FFFF" & databus(15</pre>

downto 0);

else

423

src_data <= databus; -- regardless of</pre>

data size

— both of these

425

are 32 bits

end if; — current op is branch

extaddrpass <= "10"; -- 2nd pass done

427

next\_fdc\_state <= EXEC\_READDST;

- TODO sep ALU next_fdc_state <=</pre>

429

EXEC_PUTSRCALU;

when others =>

431

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

433

report "CPU Panic — bad extaddrpass"

severity FAILURE;

end case; — extaddrpass

437

when "001" \Longrightarrow — long absolute address TODO

program_counter <= std_logic_vector(</pre>

unsigned (program_counter) + 4);

-- TODO

441

next_fdc_state <= FDC_HALT;</pre>

panic <= '1':

443

report "CPU Panic - unimplemented addressing

mode"

severity FAILURE;

445

when "100" => -- immediate data

447

if opdatasize = "11"

then -- long

449

program_counter <= std_logic_vector(</pre>

unsigned (program_counter) + 4);

451

else —word size, byte is in lower half

program_counter <= std_logic_vector(</pre>

unsigned (program_counter) + 2);

end if; — datasize

455

if current_op = OP_BRA

then

sign extend

459

src_data <= x"FFFF" & databus(15 downto 0);</pre>

else

461

src_data <= databus; -- regardless of data</pre>

size

-- both of these are 32

463

bits

end if; — current op is branch

next_fdc_state <= EXEC_READDST;</pre>

465

```

```

— TODO sep ALU next_fdc_state <=</p>

EXEC_PUTSRCALU;

467

when others =>

next_fdc_state <= FDC_HALT;</pre>

469

panic \ll '1'

report "CPU Panic - unimplemented addressing

471

mode"

severity FAILURE;

end case: —immediate or direct

473

end if: -- busdone

when others \Rightarrow

next_fdc_state <= FDC_HALT;</pre>

477

panic \ll '1';

report "CPU Panic - unimplemented addressing mode"

severity FAILURE;

end case; —src_addrcode

481

when EXEC_READDST => -- TODO direct memory

483

case current_op is

when OP_BRA =>

485

— Instruction has only one operand

— Note that for branh, we already skip this state

487

next_fdc_state <= EXEC_DOOP;</pre>

when others =>

489

case dst_addrcode(5 downto 3) is

when "000" \Longrightarrow — data register

491

this should be replaced with an integer/

unsigned

expression on the array index

case dst_addrcode(2 downto 0) is

when "000" \Rightarrow dst_data \leq data_registers (0):

495

when "001" => dst_data <= data_registers(1);

when "010" \Rightarrow dst_data <= data_registers(2);

when "011" => dst_data <= data_registers(3);

when "100" => dst_data <= data_registers(4);

499

when "101" => dst_data <= data_registers(5);

when "110" \Rightarrow dst_data \Leftarrow data_registers(6);

when "111" => dst_data <= data_registers(7);

end case; — dst_addrcode register section

503

next\_fdc\_state <= EXEC\_WAITDST:

when "001" => -- address register

— this should be replaced with an integer/

507

unsigned

— expression on the array index

case dst_addrcode(2 downto 0) is

509

when "000" => dst_data <= address_registers(0);

when "001" \Rightarrow dst_data \Leftarrow address_registers (1);

when "010" => dst_data <= address_registers(2);

when "011" \Rightarrow dst_data \Leftarrow address_registers (3);

513

when "100" => dst_data <= address_registers(4);

when "101" => dst_data <= address_registers(5);

515

when "110" => dst_data <= address_registers(6);

when "111" => dst_data <= address_registers(7);

517

end case; -- dst_addrcode register section

next_fdc_state <= EXEC_WAITDST;</pre>

when "111" => -- could be immediate or direct

521

if src_addrcode(2 downto 0) = "100"

```

```

then — immediate data invalid as destination

523

next_fdc_state <= FDC_HALT;</pre>

panic \ll '1';

525

report "CPU Panic - immediate addressing used

as dest."

severity FAILURE;

527

else

next_fdc_state <= FDC_HALT;</pre>

panic \ll '1';

report "CPU Panic - unimplemented addressing

531

mode"

severity FAILURE;

end if; — when 111

533

when others =>

535

next_fdc_state <= FDC_HALT;</pre>

panic \ll '1';

537

"CPU Panic — unimplemented addressing mode

report

severity FAILURE;

539

end case; — src_addrcode

end case; — need destination data read

541

when EXEC_WAITDST => -- TODO direct memory

543

case dst_addrcode(5 downto 3) is

when "000" \Longrightarrow — data register

545

— TODO this is necessary for the clocked registers

later

next_fdc_state <= EXEC_DOOP;</pre>

547

— TODO seperate ALU next_fdc_state <= EXEC_PUTDSTALU;</p>

when "001" \Rightarrow — address register clock

— TODO this is necessary for the clocked registers

later

next_fdc_state <= EXEC_DOOP;</pre>

551

— TODO seperate ALU next_fdc_state <= EXEC_PUTDSTALU;</p>

when others =>

553

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

555

report "CPU Panic — unimplemented addressing mode"

severity FAILURE;

557

end case; --- src_addrcode

when EXEC_DOOP =>

case current_op is

561

when OP_MOVE =>

case opdatasize is

when "11" \Rightarrow — long

rslt_data <= src_data;

565

when "10" \Longrightarrow — word

rslt_data <= dst_data(31 downto 16) &

src_data(15 downto 0);

when "01" \Longrightarrow — byte

569

rslt_data <= dst_data(31 downto 8) &

src_data(7 downto 0);

571

when others =>

next_fdc_state <= FDC_HALT;</pre>

573

panic <= '1':

report "CPU Panic - invalid operation data size"

severity FAILURE;

end case;

577

next_fdc_state <= EXEC_DOFLAGS;</pre>

```

```

when OP_BRA =>

program_counter <= std_logic_vector(</pre>

581

unsigned (program_counter)

+ unsigned(src_data));

583

- Go direct to to next instruction, no flags change

next_fdc_state <= FETCH_READINS;</pre>

585

when OP_ADD =>

587

case opdatasize is

when "11" \Longrightarrow — long

rslt_data <= std_logic_vector(unsigned(src_data)

+ unsigned(dst_data));

591

when "10" \Longrightarrow — word

rslt_data <= dst_data(31 downto 16) &

593

std_logic_vector(

unsigned(src_data(15 downto 0))

595

+ unsigned(dst_data(15 downto 0)));

when "01" \Longrightarrow — byte

597

rslt_data <= dst_data(31 downto 8) &

std_logic_vector(

599

unsigned(src_data(7 downto 0))

+ unsigned(dst_data(7 downto 0)));

when others =>

next_fdc_state <= FDC_HALT;</pre>

603

panic <= '1';

report "CPU Panic - invalid operation data size"

severity FAILURE;

607

-- TODO: this needs to be done in compnent ALU which

— also determines carry/overflow flags

next_fdc_state <= EXEC_DOFLAGS;</pre>

611

when OP_AND =>

case opdatasize is

when "11" \Longrightarrow — long

rslt_data <= src_data and dst_data;</pre>

615

when "10" \Longrightarrow — word

rslt_data <= dst_data(31 downto 16) &

(src_data(15 downto 0) and

dst_data(15 downto 0));

619

when "01" \Longrightarrow — byte

rslt_data <= dst_data(31 downto 8) &

(src_data(7 downto 0) and

dst_data(7 downto 0));

623

when others =>

next_fdc_state <= FDC_HALT;</pre>

625

panic <= '1';

"CPU Panic — invalid operation data size"

627

severity FAILURE;

end case;

629

next_fdc_state <= EXEC_DOFLAGS;</pre>

631

when others =>

next_fdc_state <= FDC_HALT;</pre>

633

panic <= '1':

report "CPU Panic - unimplemented operation"

635

severity FAILURE;

end case;

637

when EXEC_DOFLAGS =>

639

```

```

case current_op is — x/carry/overflow

when OP_MOVE | OP_AND =>

641

determine flags

— X not affected by move/and

status_register(0) <= '0'; ---carryt

status_register(1) <= '0'; --overflow

645

when OP_ADD =>

TODO: arithmetic ops set flags from ALU in EXEC_DOOP

when others =>

next_fdc_state <= FDC_HALT;</pre>

649

panic <= '1';

\begin{tabular}{lll} \textbf{report} & \textbf{"No } X/C/O & \textbf{flags} & \textbf{coded} & \textbf{for op, possible state} \\ \end{tabular}

error"

severity WARNING;

end case; — current_op for x/carry/overflow

653

case current_op is -- negative/zero - nearly all ops

655

when OP_MOVE | OP_AND | OP_ADD =>

case opdatasize is

657

when "01" \Longrightarrow — byte

if rslt_data(7 downto 0) = \times"00"

659

then ---zero

status_register(2) <= '1'; --zero

status_register(3) <= '0'; --negative

663

status_register(2) <= '0'; --zero

if rslt_data(7) = '1'

then

status_register(3) <= '1'; --negative

667

else

status_register(3) <= '0'; --negative</pre>

end if; — negative

end if; — zero

671

when "10" \Longrightarrow — word

if rslt_data(15 downto 0) = x"0000"

then ---zero

status_register(2) <= '1'; --zero

675

status_register(3) <= '0'; --negative</pre>

else

status_register(2) <= '0'; --zero

if rslt_data(15) = '1'

679

then

status_register(3) <= '1'; --negative

681

status_register(3) <= '0'; --negative</pre>

683

end if; — negative

end if; — zero

685

when "11" \Rightarrow — long

if rslt_data(31 downto 0) = x"00000000"

687

then —zero

status_register(2) <= '1'; --zero

689

status_register(3) <= '0'; --negative</pre>

else

691

status_register(2) <= '0'; --zero

if rslt_data(31) = '1'

693

status_register(3) <= '1'; --negative

695

else

status_register(3) <= '0'; --negative

697

end if; — negative

end if; -\!-\! zero

699

```

```

when others =>

next_fdc_state <= FDC_HALT;</pre>

701

panic <= '1':

report "CPU Panic - invalid operation data size"

severity FAILURE;

end case; — datasize for n/z flags

705

next_fdc_state <= EXEC_PUTRSLT;</pre>

when others =>

next_fdc_state <= FDC_HALT;</pre>

709

panic \leq '1':

"No N/Z flags coded for op, possible state error

report

severity WARNING;

end case; -- current_op for n/z

when EXEC_PUTRSLT => -- TODO direct memory

715

case dst_addrcode(5 downto 3) is

when "000" \Longrightarrow — data register

this should be replaced with an integer/unsigned

-- expression on the array index

719

case dst_addrcode(2 downto 0) is

when "000" => data_registers(0) <= rslt_data;

when "001" \Rightarrow data_registers(1) <= rslt_data;

when "010" \Rightarrow data_registers(2) \Leftarrow rslt_data;

723

when "011" \Rightarrow data_registers (3) <= rslt_data;

when "100" \Rightarrow data_registers(4) <= rslt_data;

when "101" \Rightarrow data_registers(5) <= rslt_data;

when "110" \Rightarrow data_registers(6) <= rslt_data;

727

when "111" => data_registers(7) <= rslt_data;</pre>

end case; — dst_addrcode register section

next_fdc_state <= EXEC_WAITRSLT;</pre>

731

when "001" \Rightarrow — address register

— this should be replaced with an integer/unsigned

— expression on the array index

case dst_addrcode(2 downto 0) is

735

when "000" \Rightarrow address_registers(0) <= rslt_data;

when "001" \Rightarrow address_registers (1) <= rslt_data;

when "010" => address_registers(2) <= rslt_data;

when "011" => address_registers(3) <= rslt_data;

739

when "100" \Rightarrow address_registers(4) <= rslt_data;

when "101" \Rightarrow address_registers(5) <= rslt_data;

when "110" \Rightarrow address_registers(6) <= rslt_data;

when "111" => address_registers(7) <= rslt_data;

743

end case; -- dst_addrcode register section

next_fdc_state <= EXEC_WAITRSLT;</pre>

745

when others =>

747

next_fdc_state <= FDC_HALT;</pre>

panic <= '1';

749

report "CPU Panic — unimplemented addressing mode"

severity FAILURE;

751

end case; -- src_addrcode

753

when EXEC_WAITRSLT => -- TODO direct memory

case dst_addrcode(5 downto 3) is

755

when "000" \Rightarrow — data register

– TODO this is necessary for the clocked registers

757

next_fdc_state <= FETCH_READINS;</pre>

```

```

when "001" \Rightarrow — address register clock

759

— TODO this is necessary for the clocked registers

next_fdc_state <= FETCH_READINS;</pre>

— TODO seperate ALU next_fdc_state <= EXEC_PUTDSTALU;</p>

when others =>

763

next_fdc_state <= FDC_HALT;</pre>

panic <= \ '1';

report "CPU Panic — unimplemented addressing mode"

severity FAILURE;

767

end case; ---src_addrcode

769

when FDC_HALT =>

panic \ll '1';

771

next_fdc_state <= FDC_HALT;</pre>

773

when others => -- This should not occur in final version

next_fdc_state <= FDC_HALT;</pre>

775

panic <= \ '1';

report "CPU Panic — unimplemented state" severity FAILURE;

777

end case; — end huge current state statement of doom

779

end if; — rising edge clock

end if; — reset

781

current_fdc_state <= next_fdc_state;</pre>

end process fdc_activity;

783

end behaviour;

```

# B Appendix B: DE1 Interface Source Code

#### $B.1 m68k_de1.vhd$

```

-- DE1 board <-> 68k cpu interface

— Dylan Leigh s3017239

-- Controls:

- SW 9-8: select program:

00: move/add/branch test

01: move flags test

10: move/and/branch test

11: all memory is a nop

10

-- SW 0-7: Binary clock speed selector

selects divider for auto clock

14

-- KEY3: Reset

-- KEY2: Hold for auto clock

— KEY0: Clock (for manual clock)

- Outputs:

-- HEX: Lower bytes of address and data busses

— LEDR9: panic (cpu halts until reset)

-- LEDR2-8: UNUSED

-- LEDR1 - bus write (should not be lit inside any sample programs)

— LEDRO — Bus request (should be same as busdone)

— LEDG7 — Bus done (should be same as bus request)

LEDG5-6: Bus data size (should be 10 in the sample programs)

28

— LEDG0—4: SR Flags

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity m68k_de1 is

port (

36

-- All off the board

KEY: in std_logic_vector(3 downto 0);

38

SW: in std_logic_vector(9 downto 0);

40

-- have to use "O downto O" as default pinout uses vectors for all

CLOCK_50: in std_logic;

HEX0: out std_logic_vector(6 downto 0);

44

HEX1: out std_logic_vector(6 downto 0);

HEX2: out std_logic_vector(6 downto 0);

46

HEX3: out std_logic_vector(6 downto 0);

48

LEDG: out std_logic_vector(7 downto 0);

LEDR: out std_logic_vector(9 downto 0)

50

);

end m68k_de1;

architecture mixed of m68k_de1 is

logic for displaying 4 bits as a hex digit on the 7 segment display.

component hex7seg

56

port

58

inbits: in std_logic_vector(3 downto 0);

hexout: out std_logic_vector(0 to 6)

60

);

end component;

```

```

-- clock divider

component clockdiv is

Port (

rst : in std_logic;

clk : in std_logic;

clkout : out std_logic;

68

speed : in std_logic_vector (2 downto 0)

):

70

end component;

72

component m68k_cpu_core is

74

reset: in std_logic; -- active high

clock: in std_logic;

panic: out std_logic; -- set high when CPU panics and halts

nothing changes until manually reset

80

bus controls

82

busrw: out std_logic; -- bus read/write: zero is write

busreq: out std_logic; — set to 1 to make a request from the MMU

busdone: in std_logic; — is set to 1 when request fulfilled by the MMU

busdatasize: out std_logic_vector(1 downto 0);

— 68k convention: 01: byte (8), 10: word(16), 11: long (32)

address bus

addrbus: out std_logic_vector(31 downto 0);

90

- data bus

databus: in std_logic_vector(31 downto 0);

92

- memory writes TODO databus: inout std_logic_vector(31 downto 0)

94

- outputs for debugging purposes

flags: out std_logic_vector(4 downto 0)

96

);

end component;

signal clock: std_logic;

100

signal busrw: std_logic;

signal busreq: std_logic;

102

signal busdone: std_logic;

signal busdatasize: std_logic_vector(1 downto 0);

104

signal addrbus: std_logic_vector(31 downto 0);

signal databus: std_logic_vector(31 downto 0);

106

signal flags: std_logic_vector(4 downto 0);

signal divclk: std_logic;

110

begin

cpu: m68k_cpu_core port map (

112

reset \Rightarrow not KEY(3), clock \Rightarrow clock, panic \Rightarrow LEDR(9),

busrw \Rightarrow busrw, busreq \Rightarrow busreq, busdone \Rightarrow busdone,

114

busdatasize \Rightarrow busdatasize,

addrbus => addrbus, databus => databus, flags => flags);

116

— clock divider

div: clockdiv port map (rst => not KEY(3), clk => CLOCK_50,

clkout \Rightarrow divclk, speed \Rightarrow SW(3 downto 1));

120

-- board stuff

122

-- clock manually on key0 or continuously when key1 pressed

clock \le (SW(0) \text{ and } divclk) \text{ or } (not KEY(0));

124

- LEDR(7) <= divclk; -- distracting

LEDR(4) \le clock;

126

LEDR(1) \le busrw;

LEDR(0) \le busreq;

```

```

LEDG(7) \le busdone;

LEDG(4 downto 0) \le flags;

LEDG(6 downto 5) <= busdatasize;

h0: hex7seg port map (databus(3 downto 0), HEX0);

h1: hex7seg port map (databus(7 downto 4), HEX1);

h2: hex7seg port map (addrbus(3 downto 0), HEX2);

134

h3: \ \ hex7seg \ \ port \ \ map \ \ (addrbus(7 \ downto \ 4) \ , \ \ HEX3);

136

— memory read responses

process (clock)

138

begin

if rising_edge(clock) then

140

if (busreq = '1') then

this program is all reads, word size

assert (busrw = '0')

report "CPU requested a write"

144

severity WARNING;

assert (busdatasize = "10")

146

report "Bus data size request not 16 bits"

severity WARNING;

148

case SW(9 downto 8) is — select program

150

when "00" \Longrightarrow — from fakemmu_1

memory reads

case addrbus is

when x"00000100" \Rightarrow -- move.w \#02, d1

154

databus <= "000000000000000000001111100";

^ immediate

156

__ | +__ word size

158

when \times "00000102" \Longrightarrow

160

databus <= x"00020002"; --- the #$20002

162

when x"00000104" \implies -- move.w #03, d2

databus <= "00000000000000000000010111100";

164

when x"00000106" =>

databus <= x"00030003"; -- the #$30003

166

add together

168

when \times "00000108" \Longrightarrow — add d2 to d1

databus <= "0000000000000001101001001000010";

170

^^ ^source data reg 2

+- word length

172

+ destination is data

+ which data register

+ add

176

when x"0000010A" \Rightarrow -- add #5 to d0

databus <= "0000000000000001101000001111100";

178

^ ^^ ^immediate

|+- word length

180

+ destination is data

reg

— which data register

+- add

184

when x"0000010C" \implies -- the \#$50005

databus <= x"00050005"; --- the #$50005

186

when x"0000010E" \implies -- bra $100

188

databus <= "000000000000000110000011110000";

190

+- branch

report \ "Branching \ to \ start \dots " \ severity \ NOTE;

```

```

when others =>

194

report "Memory request from unhandled location"

severity WARNING;

end case;

when "01" \Rightarrow --- from fakemmu_2

198

case addrbus is

when x"00000100" \implies -- move.w #0, d1

200

databus <= "00000000000000000001111100";

202

| | +-- data reg d1

204

+-- move

when x"00000102" \Rightarrow

databus <= x"00000000"; — the #0

208

when x"00000104" \Rightarrow -- move.w \#SDEADBEEF, d2

databus <= "00000000000000000000010111100";

210

when x"00000106" =>

databus <= x"DEADBEEF"; — the immediate data

212

more to come here when more opcodes implemented

214

— add and save in d0

216

when x"00000108" \Rightarrow -- bra $100

databus <= "000000000000000110000000000000000";

218

-- ^ -- offset all 0

+- branch

220

when x"0000010A" \implies -- bra $100

databus \ll x"0000FFF4"; — -12 decimal in word

222

report "Branching to start ... " severity NOTE;

224

when others =>

report "Memory request from unhandled location"

226

severity WARNING;

end case;

228

when "10" \Rightarrow — fakemmu_3

case addrbus is

230

when x"00000100" \Rightarrow -- move.w 10 repeating, d1

databus <= "000000000000000000001111100";

232

^ ^ ^ immediate

|  | +-- data reg d1

234

236

when x"00000102" =>

when x"00000104" \Rightarrow -- move.w 01 repeating, d2

240

databus <= "0000000000000000000010111100";

when \times "00000106" \Longrightarrow

242

databus <= "01010101010101010101010101010101";

244

— and together

when x"00000108" \Rightarrow -- and d2 to d1

databus <= "0000000000000001100001001000010";

^ ^^ ^source data reg 2

| |+- word length

+ destination is data

250

reg

⊢ which data register

+ and

252

when x"0000010A" \Rightarrow -- and 1 all to d0

254

databus <= "000000000000001100000001111100";

-- ^ ^ ^immediate

| |+- word length

```

```

+ destination is data

258

+ which data register

+ and

when \times "0000010C" \Longrightarrow

262

databus <= x"0000FFFF"; -- the #$FFFF

264

when x"0000010E" \implies -- bra $100

databus <= "000000000000000110000011110000";

266

+-- branch

268

report "Branching to start..." severity NOTE;

270

when others \Longrightarrow

report "Memory request from unhandled location"

272

severity WARNING;

end case;

274

when "11" \Longrightarrow — always nop FIXME

databus <= "0000000000000000100111001110001";

276

end case; -

busdone <= '1';

278

else — no busreq

busdone <= '0';

280

\texttt{databus} <= \, \texttt{x"00000000"};

end if; —busreq

282

end if; —clock rising edge

end process;

284

end mixed;

```

### B.2 hex7seg.vhd

```

-- vim: sw=4 ts=4 et

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY hex7seg IS

PORT

inbits: in std_logic_vector(3 downto 0);

9

hexout: out std_logic_vector(0 to 6)

11

END hex7seg;

13

ARCHITECTURE Behavior OF hex7seg IS

BEGIN

15

WITH inbits SELECT

hexout <= "1000000" WHEN "0000", -- 0

"1111001" WHEN "0001", — 1

"0100100" WHEN "0010", — 1

"0100100" WHEN "0010", — 2

"0110000" WHEN "0011", — 3

"0011001" WHEN "0100", — 4

"0010010" WHEN "0101", — 5

"0000010" WHEN "0110", — 6

21

23

"1111000" WHEN "0111", — 7

"0000000" WHEN "1000", --- 8

25

"0011000" WHEN "1001", — 9

"0001000" WHEN "1010",\ -\!\!-\!\!- a

"0000011" WHEN "1011", — b

"1000110" WHEN "1100", — c

"0100001" WHEN "1101", — d

"0000110" WHEN "1110", — e

29

31

"0001110" WHEN "1111", — f

"1111111" WHEN OTHERS;

33

END Behavior;

```

### B.3 clockdiv.vhd

```

— Adjustable clock divider

— Takes in a signal (usually the board clock), divides it by a selectable

— amount based on 3 switches.

-- vim: ts=4 sw=4 et:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL; — Two very useful

use IEEE.STD_LOGIC_UNSIGNED.ALL; — IEEE libraries

10

entity clockdiv is

Port ( rst : in std_logic;

12

clk : in std_logic;

clkout : out std_logic;

14

speed : in std_logic_vector (2 downto 0)

end clockdiv;

architecture behavioral of clockdiv is

20

signal temp: std_logic_vector(25 downto 0);

begin

22

process (clk, rst)

begin

24

if (rst = '1') then

temp <= "000000000000000000000000000000000";

26

elsif rising_edge(clk) then

temp \le temp + 1;

end if;

case speed is

30

when "000" \Rightarrow

if temp(25) = '1' then

32

clkout <= '1';

else

34

clkout <= '0';

end if;

36

when "001" =>

if temp(24) = '1' then

clkout <= '1';

40

else

clkout <= '0';

end if:

42

when "010" \Rightarrow

if temp(23) = '1' then

44

clkout <= '1';

46

clkout <= '0';

end if;

when "011" \Rightarrow

if temp(22) = '1' then

50

clkout <= '1';

else

52

clkout <= '0';

end if;

54

when "100" =>

if temp(21) = '1' then

56

clkout <= '1';

58

clkout <= '0';

end if;

when "101" =>

if temp(19) = '1' then

62

clkout <= '1';

else

64

```

```

clkout <= '0';

end if;

when "110" \Longrightarrow

if temp(18) = '1' then

clkout <= '1';

70

clkout <= '0';

end if; when "111" =>

72

if temp(17) = '1' then

clkout <= '1';

74

76

clkout <= '0';

end if;

end case;

end process;

80

end behavioral;

```

## C Appendix C: Test MMU Files

#### C.1 m68k\_fakemmu\_1.vhd

```

-- fake/test "mmu" for m68k

-- returns various values set here depending on data requested.

— test of move, add and branch

-- Dylan Leigh s3017239

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity m68k_fakemmu_1 is

end m68k_fakemmu_1;

architecture mixed of m68k_fakemmu_1 is

component m68k_cpu_core is

14

port (

reset: in std_logic; — active high

16

clock: in std_logic;

18

panic: out std_logic; -- set high when CPU panics and halts

— nothing changes until manually reset

20

-- bus controls

busrw: out std_logic; — bus read/write: zero is write

busreq: out std_logic; — set to 1 to make a request from the MMU

busdone: in std\_logic; — is set to 1 when request fulfilled by the MMU

busdatasize: out std_logic_vector(1 downto 0);

26

-- 68k convention: 01: byte (8), 10: word(16), 11: long (32)

28

-- address bus

addrbus: out std_logic_vector(31 downto 0);

30

-- data bus

databus: inout std_logic_vector(31 downto 0);

-- for debugging

flags: out std_logic_vector(4 downto 0)

36

);

end component;

38

signal reset: std_logic;

40

signal clock: std_logic;

signal busrw: std_logic;

signal busreq: std_logic;

signal busdone: std_logic;

44

signal busdatasize: std_logic_vector(1 downto 0);

signal addrbus: std_logic_vector(31 downto 0);

46

signal databus: std_logic_vector(31 downto 0);

48

begin

cpucore: m68k_cpu_core

50

port map (

reset => reset , clock => clock , -- panic => null

-- Note: we ignore panic as in simulation the CPU core will

-- raise an assertion itself on a panic

busrw => busrw, busreq => busreq, busdone => busdone,

busdatasize \Rightarrow busdatasize, addrbus \Rightarrow addrbus, databus \Rightarrow databus

56

);

58

busread: process (busreq)

begin

60

if rising_edge(busreq)

then

62

```

```

assert (busrw = '0')

report "Bus requested a read."

severity WARNING;

assert (busdatasize = "10")

report "Bus data size request not 16 bits."

severity WARNING;

68

-- memory reads

70

case addrbus is

when x"00000100" \Rightarrow -- move.w #02, d1

72

databus <= "00000000000000000001111100";

-- ^ ^ ^ immediate

-- | | +- data reg d1

+-- word size

+-- move

when \times "00000102" =>

databus <= x"00020002"; --- the #$20002

80

when x"00000104" \implies -- move.w #03, d2

databus <= "0000000000000000000010111100";

82

when \times "00000106" \Longrightarrow

databus <= x"00030003"; -- the #$30003

— add together

when x"00000108" \Rightarrow -- add d2 to d1

databus <= "0000000000000001101001001000010";

^^ ^source data reg 2

| |+- word length

90

\mid + destination is data reg

— which data register

92

+ add

94

when \times "0000010A" \Longrightarrow — add #5 to d0

databus <= "0000000000000001101000001111100";

96

^ ^^ ^immediate

| |+- word length

| +- destination is data reg

+\!\!\!- which data register

100

+ add

102

when x"0000010C" \implies --- the \#$50005

databus <= x"00050005"; --- the #$50005

104

when x"0000010E" \implies -- bra $100

106

databus <= "000000000000000110000011110000";

— +── branch

report "Branching to start..." severity NOTE;

110

when others =>

112